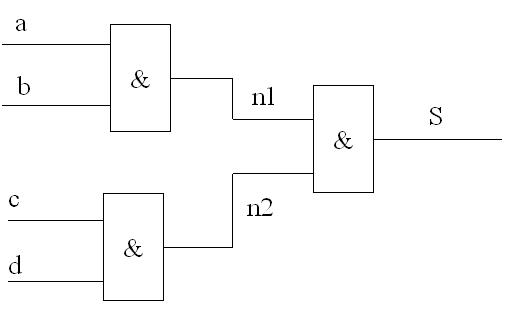

Si on a remarqué

dans la bibliothèque des ressources, une fonctionnalité

qui correspond à la fonction ET à

2 entrées. Son prototype est le suivant :

module And2 (a, b, S) ;

Par nos compétences

et acquis précédents, nous savons mettre

en cascade les fonctions ET pour obtenir des ET à

plus d’entrées. C'est ce que l'on retrouve

sur le logigramme ci-dessous :

Des

liaisons internes (n1 et n2) sont nécessaires sans

pour cela qu’il s’agisse d’entrée

ou de sortie. Ces connexions seront déclarées

du type wire. Ce sont des liaisons équipotentielles ou des fils.

Un « wire » est

une interconnexion interne simple, une équipotentielle.

Ainsi on pourra obtenir le programme suivant

:

module ET4 (a, b, c,

d, S) ;

input a, b, c, d ;

output S ;

wire n1, n2 ;

And2 ET1 (a, b, n1) ; // On prend un composant du

type And2 que l’on nomme ET1

And2 ET2 (c, d, n2) ;

And2 ET3 (n1, n2, S) ;

endmodule

Explication

: And2 ET2 (c,d,n2); revient à avoir

pris un composant appelé ET2 de type And2 (ET

à 2 entrées) et avoir relié ses

entrées à c et d et sa sortie à

n2.

Conseil : les indentations

et sauts de ligne ne sont pas obligatoires, mais apportent

une réel confort de lecture

Remarque : ce programme réalisé

en technologie classique avec des portes ET à

2 entrées génèrerait des temps

de propagation doublés. Ce ne sera pas

le cas avec les composants programmables : l'implantation

réelle donnera la même fonctionnalité,

mais la description n'impose pas la réalisation.

Ainsi, le fichier contenant ce qui suit donne le même

résultat à la compilation.

module ET4 (a, b, c, d, S); input

a, b, c, d; output S; wire n1, n2; And2 ET1(a, b,

n1); And2 ET2(c, d, n2); And2 ET3(n1, n2, S); endmodule

Il n'est pas aussi

facile à lire et à comprendre, c'est

pourquoi, on conseille de mettre une instruction par

ligne et de pratiquer avec des indentations pour les

structures de contrôle. De même, il peut

être plus difficile à débogguer

en cas d'erreur.