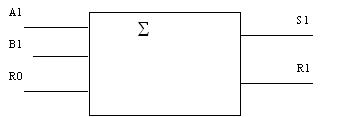

Un additionneur 1 bit complet est un additionneur

générique permettant le cascadage (opération

sur plusieurs bits) et qui fournit un résultat permettant

d'étendre l'opération.

Il possède de ce fait 3 entrées

que l'on nommera A1, B1 et R0 et 2 sorties S1 et R1.

Les entrées A1, B1 sont les 2 opérandes

à additionner à une

retenue venue du calcul précédent.

L'indice 1 indiquera le rang de l'opération

et 0 la provenance d'un résultat précédent.

Pour les sorties, la somme de 3 termes sur

1 bit tient obligatoirement sur 2 bits : S1 est la somme

de rang 1 et R1, la retenue générée

(le bit de poids fort du résultat).

|

R0

|

A1

|

B1

|

R1

|

S1

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

0

|

1

|

|

0

|

1

|

0

|

0

|

1

|

|

0

|

1

|

1

|

1

|

0

|

|

1

|

0

|

0

|

0

|

1

|

|

1

|

0

|

1

|

1

|

0

|

|

1

|

1

|

0

|

1

|

0

|

|

1

|

1

|

1

|

1

|

1

|

Le symbole (non normalisé) pourra

avoir l'allure suivante :

Le problème peut être résolu

de différentes façons :