La lecture du symbole nous permet

de voir qu'il s'agit d'un compteur-décompteur

synchrone BCD avec chargement synchrone. Il possède

des entrées de validation et une sortie de

retenue anticipée (en comptage comme en décomptage).

Son fonctionnement :

- il compte sur un front montant

de clk, quand il est valide (enp et ent à

1), avec ud_bar à 1 et load à 1,

- il décompte sur un front

montant de clk, quand il est valide (enp et ent

à 1), avec ud_bar à 0 et load à

1,

- il charge e en Q sur un front montant

de clk quand il est valide (enp et ent à

1) et que load est à 0,

- La retenue anticipée se

positionne à 0 quand on atteint 9 en comptage

et 0 en décomptage, à condition d'avoir

ent valide.

La solution peut être la suivante

:

module U74168 (load_bar, ud_bar,

ent, enp, clk, e, Q, RCO_bar) ;

input load_bar, ud_bar, ent, enp,

clk ;

input [3 : 0] e ;

output RCO_bar ;

output [3 : 0] Q ;

reg RCO_bar ;

reg [3 : 0] Q ;

always @ (posedge clk)

if (ent)

if ((ud_bar && (Q ==9

)) || (!ud_bar && (Q == 0)))

RCO_bar = 0 ;

else

RCO_bar = 1 ;

always @ (posedge clk)

if (enp && ent)

if (! load_bar)

Q = e ;

else

if (ud_bar)

begin

Q = Q+1 ;

if (Q == 10)

Q = 0;

end

else

begin

Q = Q-1 ;

if (Q == 15)

Q = 9 ;

end

endmodule

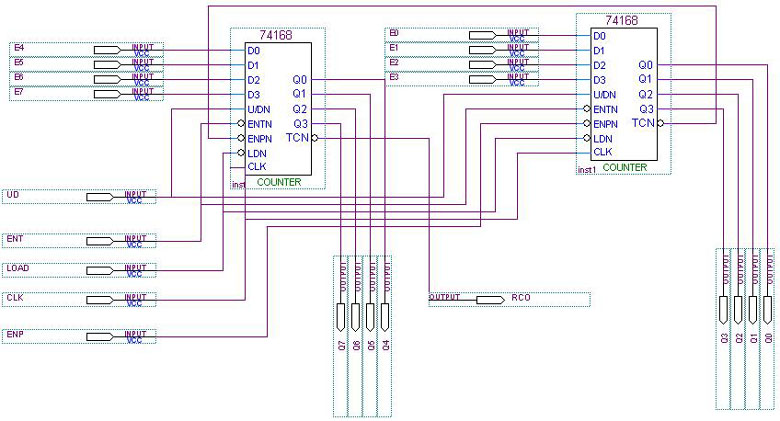

La solution pour un passage à

8 bits avec des composants 74168 donne le schéma

suivant (schéma réalisé avec

l'outil QUARTUS)

Le passage à 8 bits par programme

n'implique pas de gros changements.

En instanciant le module précédent.

Ceci revient à faire le schéma.

module U74168s_8bits (load_bar, ud_bar,

ent, enp, clk, e, Q, RCO_bar) ;

input load_bar, ud_bar, ent, enp,

clk ;

input [7 : 0] e ;

output RCO_bar ;

output [7 : 0] Q ;

wire rco_unit ;

U74168 Compteur1(load_bar, ud_bar,

ent, rco_unit, clk, e[7:4], Q[7:4], RCO_bar) ;

U74168 Compteur2(load_bar, ud_bar,

ent, enp, clk, e[3:0], Q[3:0], rco_unit) ;

endmodule

En synthétisant l'ensemble,

on obtient la description complète du fonctionnement

du compteur modulo 100 :

Il faut compter et décompter

en BCD de 0 jusqu'à 99 en fonction de l'entrée

de comptage-décomptage. Il faut de plus gérer

une retenue (carry) à 99 en comptant et à 0 en

décomptant.

module U74168s_8bits (load_bar, ud_bar,

ent, enp, clk, e, Q, RCO_bar);

input load_bar, ud_bar, ent, enp,

clk ;

input [7 : 0] e ;

output RCO_bar ;

output [7 : 0] Q ;

reg RCO_bar ;

reg [7 : 0] Q ;

always @ (posedge clk)

if (ent)

if ((ud_bar && (Q ==8'h99

)) || (!ud_bar && (Q == 0)))

RCO_bar = 0 ;

else

RCO_bar = 1 ;

always @ (posedge clk)

if (enp && ent)

if (! load_bar)

Q = e ;

else

if (ud_bar)

begin

Q = Q+1 ;

if ((Q & 8'h0f) ==

10) // ou 8'h0a

begin

Q = Q +6 ;

if ((Q & 8'hf0)==

8'ha0)

Q = 0 ;

end

end

else

begin

Q = Q-1 ;

if ((Q && 8'h0f)

== 15) // ou 8'h0f

begin

if (Q == 8'hff)

Q = 8'h99 ;

else

Q = Q - 6 ;

end

end

endmodule

On peut très facilement en

faire un compteur paramétrable.

Pour tout comptage particulier (en

dehors du compteur qui va de 0 à 99), il sera

beaucoup plus pratique de faire une description comportementale

plutôt que d'envisager le schéma.