5.3.1 PRESENTATION

La présentation

est commune aux 3 exercices sur le CAN

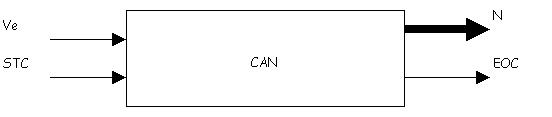

Un convertisseur Analogique Numérique possède

2 entrées et 2 sorties. Les entrées sont la

tension analogique d'entrée (Ve) et l'ordre de début

de conversion (STC). Les sorties sont sont regroupées en un mot de N bits représentatif

de la grandeur analogique (image de Ve) et un signal logique

EOC indiquant la fin de conversion et la disponibilité

du résultat. Le temps de conversion

n’est pas nul.

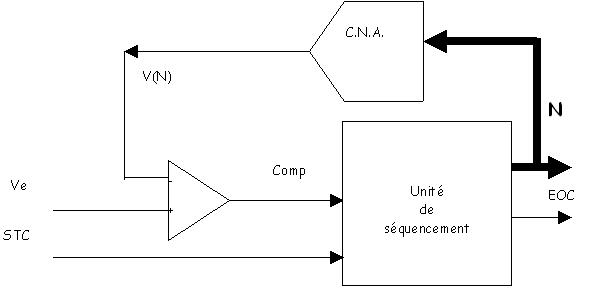

Le principe du CAN retenu est le

suivant : comparer la tension de sortie d’un CNA à

celle de la tension analogique à convertir inconnue. Lorsque

qu'elle est atteinte par valeur croissante ou décroissante, la

sortie du comparateur bascule. On peut affirmer que le nombre

présent sur le CNA est proche de la valeur numérique

désirée. Pour cela, l’unité de

séquencement fournit une suite de valeurs numériques Nk.

La conversion est déclenchée par le passage à 1 de

STC (Start Conversion). Le signal EOC (End of Conversion) passant

à 1 indique qu’une valeur N est disponible. On proposera,

dans ce travail, plusieurs stratégies pour atteindre le

résultat escompté. L'efficacité des

méthodes sera comparée.

Remarques :

- le CAN réalisé dispose de 2 entrées

Ve (analogique) et STC (logique) et de 2 sorties logiques

N sur 8 bits (résultat de la conversion) et EOC,

- le CNA a une dynamique de 0 à 5 volts. Il fournit

un résultat sur 8 bits : la valeur 0 correspond à

0 volt et 255 à 5 volts. Le CAN aura donc les mêmes

caractéristiques que le CNA,

- tous les signaux logiques sont compatibles TTL, même

la sortie du comparateur,

- l’unité de séquencement sera réalisée

à partir d’un CPLD,

- le langage retenu est Verilog.

On dispose d’une maquette

composée d’un CNA 8 bits (un CNA est un composant

très facile à réaliser) et d’un

comparateur.

Les 3 projets CAN qui suivent permettent d’envisager plusieurs

stratégies pour l’unité de séquencement. Ainsi

il est demandé de faire l’analyse et le découpage

en blocs fonctionnels pour chacune des 3 stratégies.

Chacun des signaux internes devra être défini

et chacune des fonctions devra être précisément

décrite.

On dispose d’une horloge (1MHz) sur

la carte pour cadencer la conversion.

Nota : La sortie « Sortie Analogique » présente

sur la photo n'est autre que la sortie logique du comparateur (Comp).

5.3.2 C.A.N. à RAMPE NUMERIQUE

La tension V(N) croît de 0 jusqu’à atteindre

Ve. A ce moment, c’est la fin de la conversion.

Dans le cadre de cette méthode, suite

à la commande STC (mise à 1 impulsionnelle),

on incrémente d'une unité la grandeur N en partant de la valeur

0. La tension V(N) deviendra égale

ou supérieure à Ve, le comparateur basculera

et passera à 0. On mémorisera la valeur N

et on indiquera la fin de conversion en positionnant EOC à

1.

Analyser, coder, simuler, débogguer et valider.

En utilisant l'horloge

1MHz, déterminer les temps de conversion pour la

suite (1Volt, 2.5 volts, 4 volts, 3volts).

Conclure sur la valeur et la dépendance

du temps de conversion.