3.1.1 Les noms de fichiers

Le programme doit porter

obligatoirement l’extension des fichiers Verilog (xxx.v). Il peut être édité

avec un éditeur simple gérant un

fichier ASCII élémentaire.

On doit créer un projet portant le même nom (le projet est un répertoire, il pourra comporter

plusieurs fichiers avec d’autres

noms).

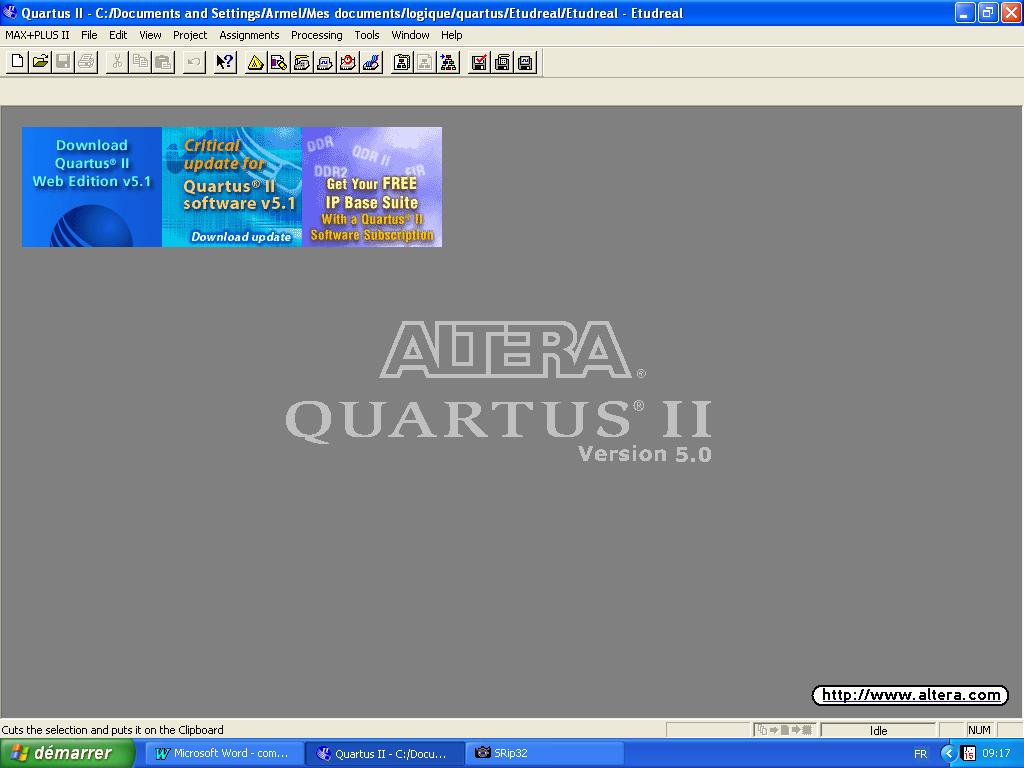

Lancer

en premier l'exécution du logiciel :

Il apparaît alors une fenêtre

ayant la présentation suivante :

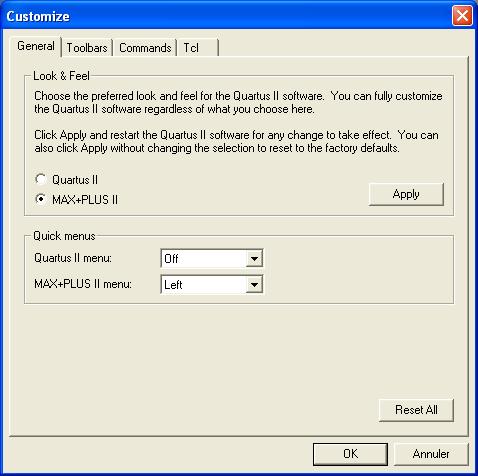

Si à l'installation

vous avez un autre environnement, aller dans la barre de

menu, sélectionner Tools -> Customize ...

Dans l'onglet General,

cocher Look anf Feel : MAX+PLUS II qui

présente un environnement plus convivial identique

à celui décrit par la suite.

3.1.2 Ouvrir le projet

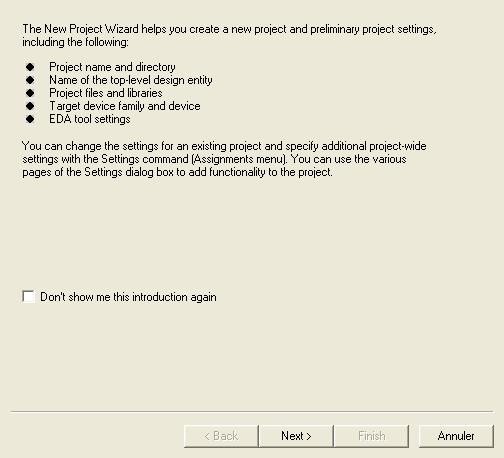

Pour créer un nouveau projet, dans

le menu File, choisir d’ouvrir un

nouveau projet : New Project Wizard ….

Une première fiche apparaît

:

que l’on passe : elle ne permet aucune saisie, ni modification. Elle

nous informe sur le contenu des fenêtres à venir :

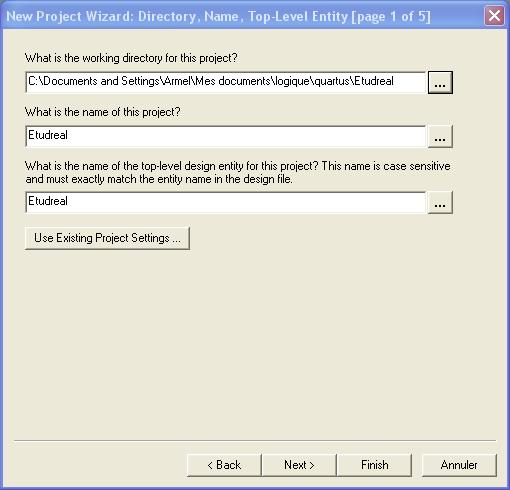

Dans la cette seconde

fiche, on prendra soin de :

- donner le chemin d'accès propre au projet (1ère

ligne),

- donner un nom

au projet (par défaut identique au répertoire),

- donner le nom

du module qui sera utilisé (par défaut identique

à celui de la 2ème ligne).

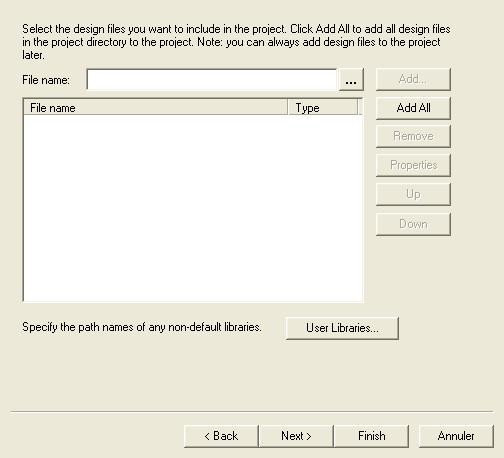

La 3ème fiche permettra

d'inclure éventuellement des fichiers ressources

(elle restera vide la plupart du temps dans nos applications).

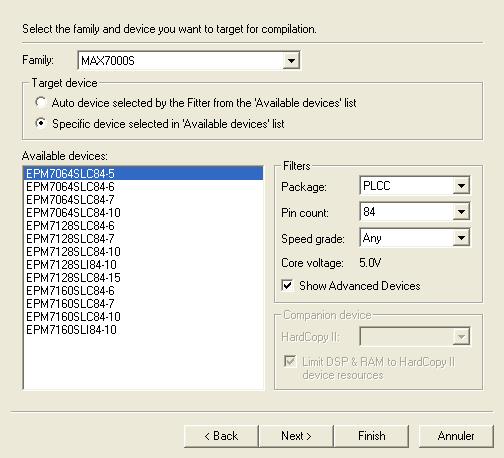

La

4ème fiche permet de désigner la cible. On choisira la

référence du composant cible. Dans la phase de

simulation, on prendra un composant suffisamment dimensionné

pour intégrer le programme.

Remarque : la cible pourra

être changée ultérieurement pour migrer

éventuellement vers une plus grande capacité ou une plus petite.

Il sera impératif de recompiler le projet afin qu'il

puisse être placé dans la cible.

La désignation des

composants de la série 7000:

Exemple : EPM7064 SLC 84-5 désigne

un composant de la série 7000S possédant :

- 64 cellules internes,

- 84 broches sur le boitier,

- un temps de propagation de 5 ns

Remarque : le choix de composant étant mémorisé, il est possible de faire le choix

Finish qui nous envoie directement à

la dernière fiche.

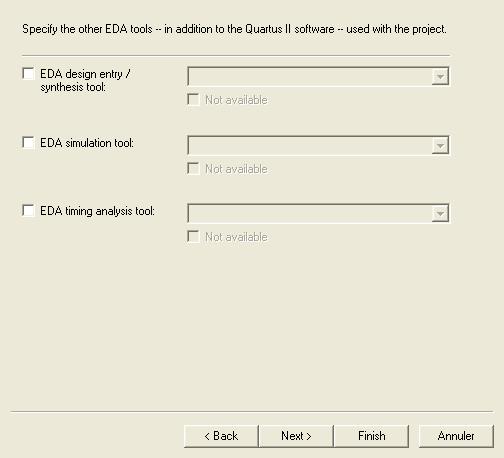

L'avant dernière

fiche permet de choisir d'autres outils de développement

que ceux fournis par ALTERA. On pourra

ainsi choisir un autre outil de synthèse, de simulation

ou d'analyse temporelle. Sauf pour un choix personnel, les

outils proposés sont amplement suffisants pour l'usage

requis dans ce module.

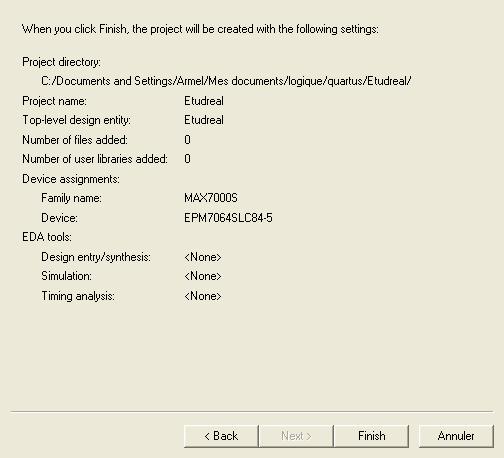

La dernière fiche récapitule

l'ensemble des choix effectués.

Ne pas se tracasser des None

pour les EDA Tools. Ceci signifie que vous

prenez les éléments proposés par défaut

et non pas aucun.

Par la suite, pour ouvrir un

projet, il suffit de choisir File -> Open Project...

La

démonstration

3.1.3 Editer le fichier source

Une fois le projet

crée, il faut ouvrir un nouveau fichier : File

-> new…

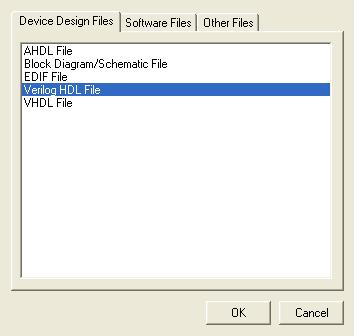

On choisit alors l’onglet

Device Design Files et un fichier Verilog

HDL File.

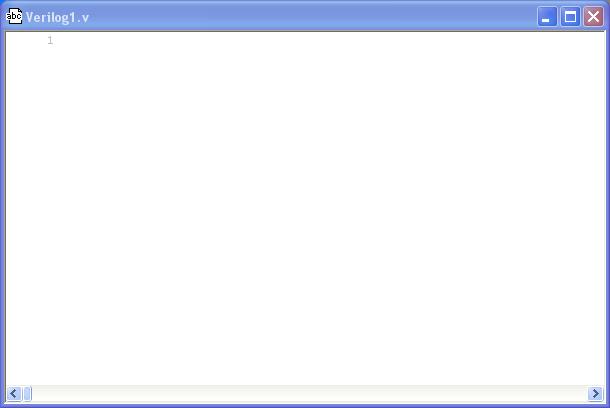

On obtient alors un fichier vide à nommer.

Ce fichier devra avoir le nom imposé

dans la 2nde fiche. En prenant l'option File ->

Enregistrer sous..., on sauvera normalement automatiquement

sous le nom correct (ici : Etudreal.v).

Il suffit maintenant de saisir son programme.

Remarque

: le fichier pourra comporter plusieurs modules, mais un

module aura obligatoirement le même nom que celui du projet, ce sera le

module application. Il pourra ne comporter

qu’un module.

Remarque : il sera

possible d'ajouter ou de retirer des fichiers à notre

projet en allant dans

Project, ==> Add/Remove Files in Project à partir de la barre de menu.

Remarque : les bibliothèques

de composants génériques ou ceux de la série

74XX sont par défaut directement disponibles (pas

d'inclusion nécessaire).