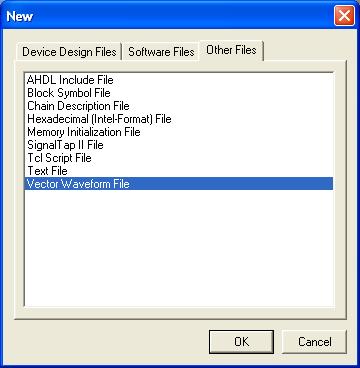

Il faut maintenant vérifier

la réalisation par une simulation. Un nouveau

fichier doit être créé.

Pour cela dans

la barre de menu : choisir File -> New …

Après avoir

choisi l’onglet « Other Files

», on choisit Vector Waveform File.

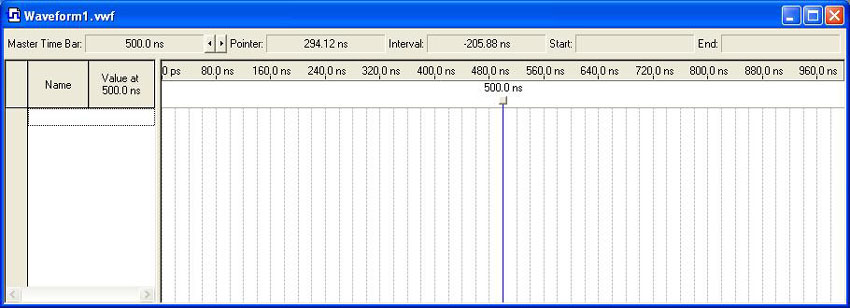

Il apparaît une zone qui permet

l’édition de signaux. Elle porte le nom

waveform.vwf par défaut.

Ce fichier doit être

enregistré sous le même nom que

le fichier module principal ou le projet

et comporter l’extension .vwf

En premier lieu, il est nécessaire

de fixer la durée de la simulation. Il faut

dans la barre de menu sélectionner : Edit -> EndTime …

Il apparait la fenêtre

suivante que l'on complète.

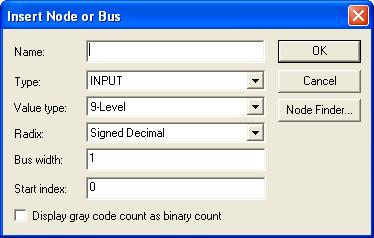

Ensuite il faut aller

chercher la liste des équipotentielles, des

entrées et sorties à faire apparaître

lors de la simulation. Ceci se fait à partir

de la fenêtre de simulation, par un clic droit

dans la zone blanche sous Name.

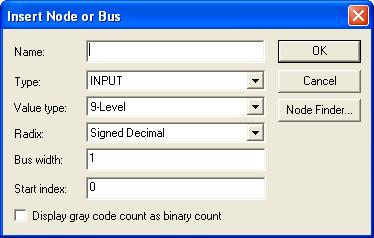

Il surgit alors un menu

dans lequel apparaît : Insert Node or

Bus… que l’on choisit

On choisit Node

Finder...

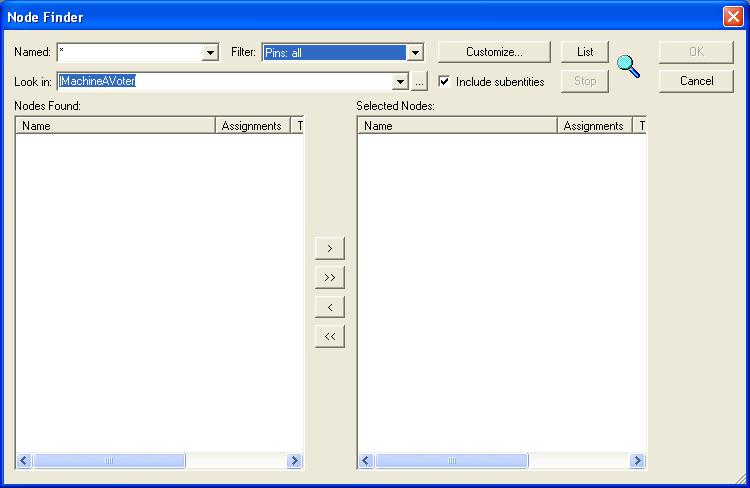

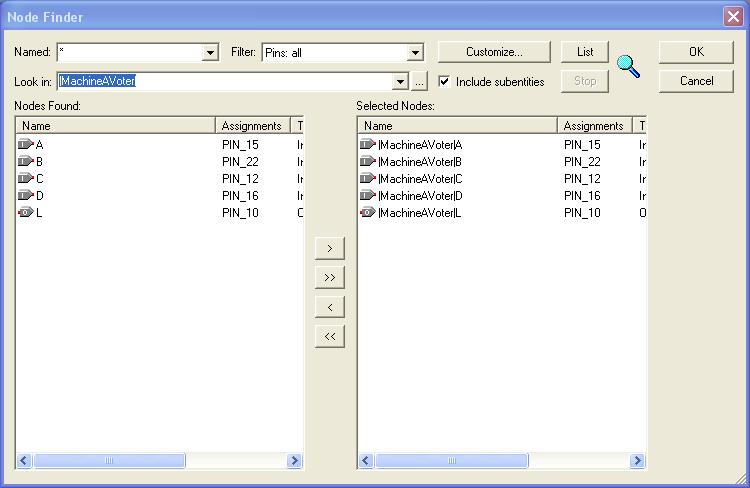

On se retrouve avec une

fenêtre qui nous permet dans :

- Filter de choisir

par options (broches assignées, toutes entrées-sorties,

registres),

- Customize permet

de personnaliser ces choix,

- List fait apparaître

dans la fenêtre de gauche les choix possibles.

Grâce aux flèches

entre les 2 fenêtres, on fait passer les connections

à visualiser dans notre espace pour la simulation.

.

.

Lorque tous les choix

sont faits, on clique sur OK

Puis à nouveau

sur OK

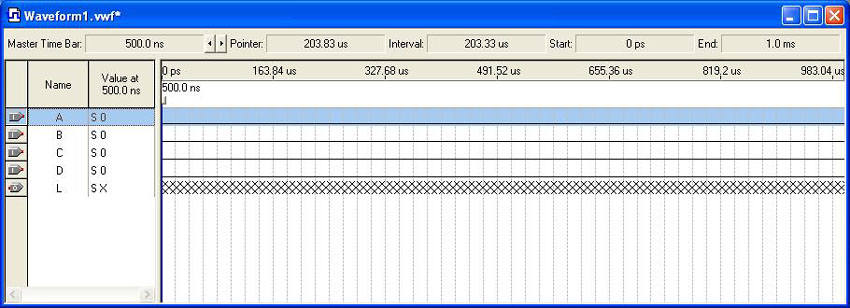

On peut faire apparaître

des zones temporelles à 1 ou à 0 en

validant la ligne (faire un clic sur l’icône

de l’entrée à définir),

puis réaliser des « cliquer-glisser

» en utilisant les icônes situés

à gauche tels que :

- la mise à 0 (

)

)

- la mise à 1 (

),

),

- l’inversion (

),

),

- le signal aléatoire

(

).

).

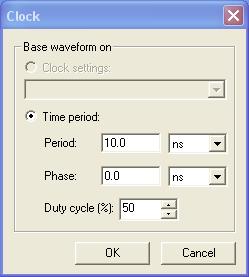

Il est aussi possible

de générer des signaux périodiques

:

- signal d’horloge (  )

)

On accède alors à

la fiche suivante qui permet de fixer :

- la période du signal (Period),

- le retard au démarrage (Phase),

- le rapport cyclique (Duty Cycle).

- valeurs

numériques (  )

)

Il arrive que l’on ait

des signaux numériques à entrer,

fiche ci-dessous le permet.

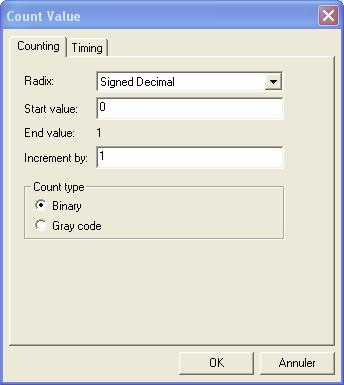

Avec l’onglet Counting,

on fixe la base (Radix), la valeur de départ

(Start value) et l’incrément

(Increment by) ainsi que le type de codage

binaire (Count Type)

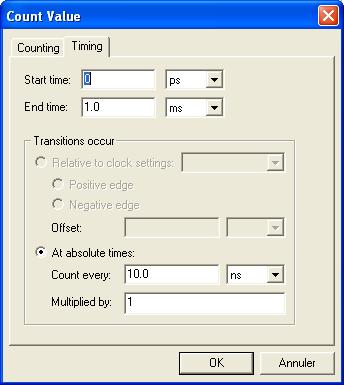

Avec l’onglet Timing,

on fixe l’instant de départ du

comptage (Start Time),

la fin de comptage (EndTime)

et la période de transition (Transitions occur).

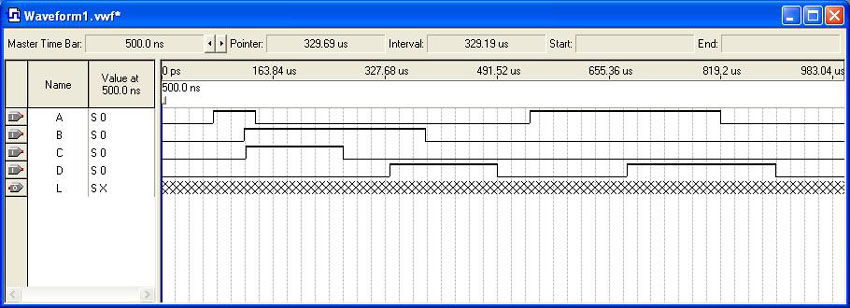

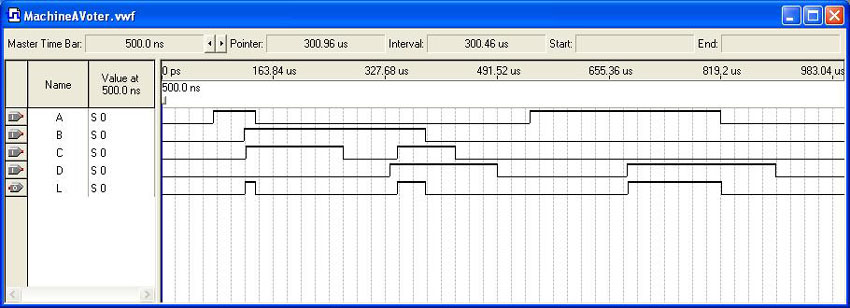

Les signaux étant

définis, on obtient un jeu de simulation pouvant

avoir l'allure suivante :

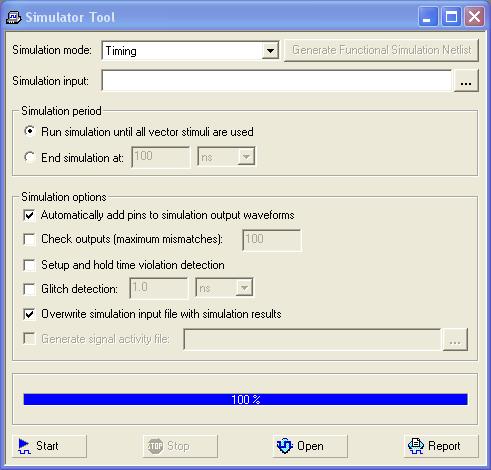

Il faut ensuite lancer

le simulateur : Tools -> Simulator Tool...

à partir de la barre de menu ou utiliser l'icône

simulateur dans la barre d'outils :

En cliquant sur «

Start », on lance la simulation.

En cliquant par la

suite sur « Open », on

ouvre la fenêtre consignant le résultat

de la simulation.

Vous avez fait votre

première simulation ...

La

démonstration

Vous pouvez modifier

l'état d'entrées ou de sorties, ajouter

des élements à visualiser, modifier

votre programme, simuler de nouveau (mettre au

point).

Pour votre compte

rendu, il est fort agréable de pouvoir intégrer

les chronogrammes. La version gratuite de Quartus

ne vous permet pas de faire directement un « copier-coller

» vers votre éditeur de texte préféré.

Ceci reste très aisé en utilisant un

outil freeware tel que SRIP32. Pour le télécharger,

cliquer ici.

Ne pas oublier de

recompiler après toute modification.