La méthode :

On peut remarquer que c'est l'écart

de temps entre les 2 signaux d'entrée

qui va conditionner la fréquence dans le haut-parleur. On

propose de mesurer ce temps (en microsecondes). Ensuite, on

génèrera une fréquence dépendante de ce

temps (on peut voir le lien direct entre ce temps et la période

du signal à générer : identique). De même,

un seuil sera à déterminer pour ne pas émettre de

son. Connaissant un nombre correspondant à un nombre de

microsecondes, il est facile avec une horloge à 1MHz, de

gérérer un signal en créneaux de rapport cyclique

le plus proche possible de 0,5.

En allant plus loin dans l'analyse, les

blocs fonctionnels et leur description plus fine apparaissent

naturellement.

L'analyse :

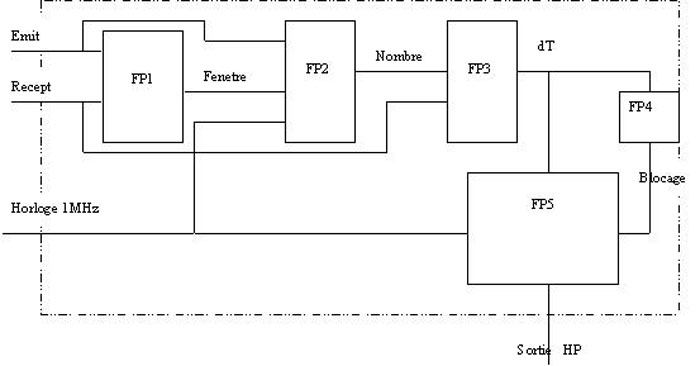

Notre analyse induit un découpage en fonctions principales

(FPn) qui sont présentées sur

la figure suivante :

Remarque : les signaux internes aux pointillés ne

sont pas connectés aux broches du composant CPLD.

FP1 est une fonction qui

reçoit les informations Emit et Recept. Elle délivre un

signal à 1 dès l’arrivée de

l’impulsion Emit et ce jusqu’à

l’arrivée de Recept (c’est la fenêtre de

comptage). Ce signal s'appellera « Fenetre ».

FP2 est une fonction qui compte la

durée de « Fenetre » en microsecondes. Sa

sortie est appelée « Nombre ». Cette fonction

reçoit le signal d’horloge Horl, « Fenetre

» et Emit. Elle est remise à 0 par l’arrivée

de Emit.

FP3 mémorise « Nombre » à

l’arrivée de Recept, ce qui génère

la grandeur « dT ».

FP4 est une fonction qui positionne la sortie

« Blocage » à 1 lorsque « dT » est supérieur à

6600 et à 0 dans les autres cas.

FP5 est une fonction qui génère

un signal en créneaux qui sera dirigé vers

l’amplificateur d’un Haut-Parleur. Pour cela, on utilise

l’entrée numérique « dT », l’horloge

Horl et l’information de blocage. L’entrée

« Blocage » au niveau 1 doit empêcher le Haut-Parleur d’émettre

un son (le signal de sortie ne change pas). Dans l’autre

cas, il faut générer un signal

en créneaux de période (dT)µs dans le Haut-Parleur. Le rapport

cyclique doit être le plus proche possible de 50%.

Conclusion :

Même avec une idée

de départ paraissant complexe, la réalisation du dispositif

est aisée. Comme partout, l'analyse est un préalable

incontournable qui ne doit pas être négligé.