La méthode :

Dans le sujet, on dispose

d'un CNA 8 bits, la résolution de notre convertisseur

CAN est donc de 8 bits. La grandeur de sortie de notre séquenceur

sera 8 bits.

On doit remettre la sortie EOC à

0 quand on a le signal STC à 1 et la positionner

à 1 quand a atteint la valeur N (basculement du comparateur)

==> la conversion est terminée. Cette durée

sera aussi notre fenêtre de mesure. On utilisera une

bascule pour autoriser le comptage. Le passage à

1 de EOC entrainera le blocage du compteur.

On devra disposer:

- d'un compteur modulo 256,

- d'une bascule pour notre fenêtre

de comptage.

L'analyse :

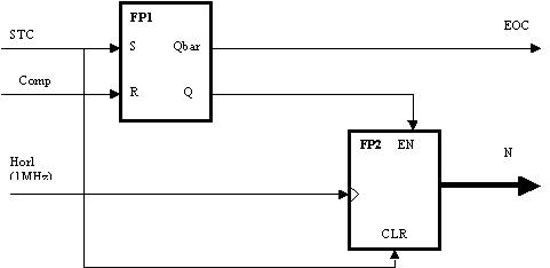

Ceci nous amène à une

description correspondant au schéma de

principe suivant :

FP1 est une bascule RS

FP2 un compteur synchrone 8

bits avec 2 entrées EN (autorisation de comptage)

et CLR (remise à zéro).

Rappel : le compteur

est modulo 256 avec une valeur initiale 0.

Conclusion sur le temps de conversion :

Le temps de conversion est ici directement proportionnel à la tension à convertir. Il atteint, dans le cas le plus défavorable,

la valeur de 256 fois la période de l'horloge.